# BIOE40002 – Computer Fundamentals and Programming 1

Part I – Digital Logics, Lab 6

Binghuan Webster Li | Department of Bioengineering

binghuan.li19@imperial.ac.uk

February 24, 2022

### Meme of the day...

## Today's Schedule

- Recap (~ 10 mins)

- Selectors and multiplexers

- Arithmetic-logic units

- Lab exercises 12 and 13

- Quick summary

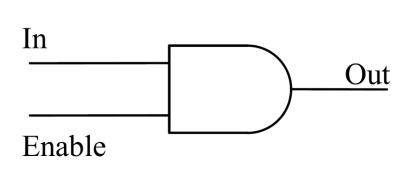

### AND gates as selectors

| Enable | In | Out |

|--------|----|-----|

| 0      | 0  | 0   |

| 0      | 1  | O   |

| 1      | 0  | O   |

| 1      | 1  | 1   |

- When *Enable* is set to 1, output follows input

- When *Enable* is set to 0, output would remain 0 regardless of the value of input

- Selector

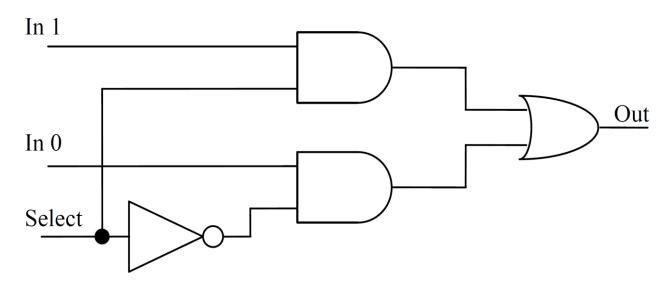

### 2 × 1 multiplexer

### Imperial College London

| • | When Select | ct is set to | 1, output | follows input |

|---|-------------|--------------|-----------|---------------|

|   | channel 1 ( |              | •         | •             |

• When *Select* is set to 0, output follows input channel 0 (*Ino*)

•  $2 \times 1$  multiplexer  $= \frac{1}{5}$

| _    | Out | Select | In 1 | In 0 |

|------|-----|--------|------|------|

| _    | 0   | 0      | 0    | 0    |

| In 0 | 0   | 0      | 1    | 0    |

|      | 1   | 0      | 0    | 1    |

|      | 1   | 0      | 1    | 1    |

| )    | 0   | 1      | 0    | 0    |

| In 1 | 1   | 1      | 1    | 0    |

| In 1 | 0   | 1      | 0    | 1    |

|      | 1   | 1      | 1    | 1    |

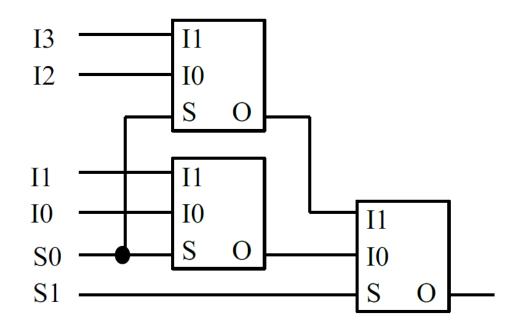

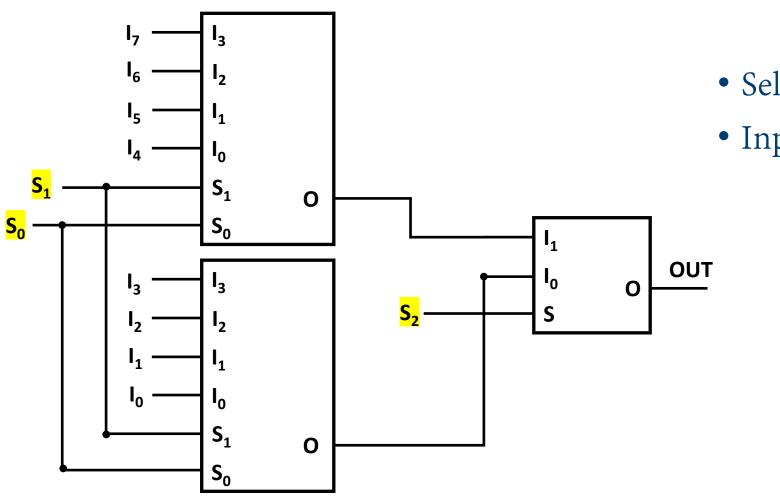

### 4 × 1 multiplexer

- 2 selector terminals So, S1

- Select the signal from *I0*, *I1*, *I2*, *I3*

• E.g., S0=1, S1=1; O=I3

It is your turn to design a  $8 \times 1$  multiplexer with two  $4 \times 1$  multiplexers and one  $2 \times 1$  multiplexer!

### Task 12 – Design an 8x1 multiplexer

- Selection terminal: *So-S2*

- Input signal: *Io-I*7

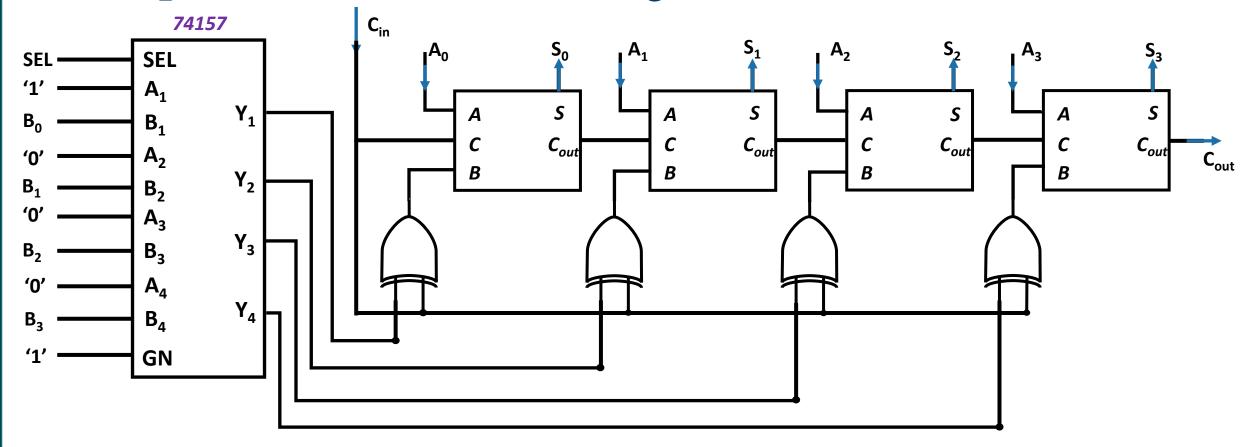

### 4-operation arithmetic-logic units

| Instruction 0 Set_B=1 | Instruction 1 Subtract | Operation |                                                   |

|-----------------------|------------------------|-----------|---------------------------------------------------|

| 0                     | 0                      | ADD       | • ADD = $A+B$                                     |

| 0                     | 1                      | SUB       | • $SUB = A + (-B)$                                |

| 1                     | 0                      | INC       | • INC = $A+1 \rightarrow \text{set } B=1$         |

| 1                     | 1                      | DEC       | • DEC = $A + (-1) \rightarrow \text{set } B = -1$ |

- Q: how to design such a 4-operation ALU with a 4-bit addition/subtraction machine and a multiplexer?

- *A*: think about how we set the input *B*!

### 4-operation arithmetic-logic units

- $A_4A_3A_2A_1 = 0001 \rightarrow \text{instruction 0 (Set\_B=1)} \rightarrow \text{INC, DEC}$

- $B_4B_3B_2B_1 = 4$ -bit inputs  $\rightarrow$  ADD, SUB

- $C_{in} \rightarrow instruction 1 (subtraction)$

|              | SEL = 0 | SEL=1 |

|--------------|---------|-------|

| $C_{in} = 0$ | INC     | ADD   |

| $C_{in}=1$   | DEC     | SUB   |

### Questions?

That's it for now.

You can now proceed to the Exercise 12 and 13.

# Summary of Digital Logics labs

#### Imperial College London

- *Lab 1*: Boolean algebra, logic gates and identities, p-/n-CMOS as switches

- Lab 2: Binary numbers, binary addition, half-adders, full-adders

- Lab 3: 4-bit addition machine, signed binary representation

- Lab 4: binary subtraction and 4-bit subtraction machine

- *Lab 5*: 4-bit addition-subtraction machine, multiplexers

- *Lab 6*: 4-operation arithmetic-logic unit

Thoughts?